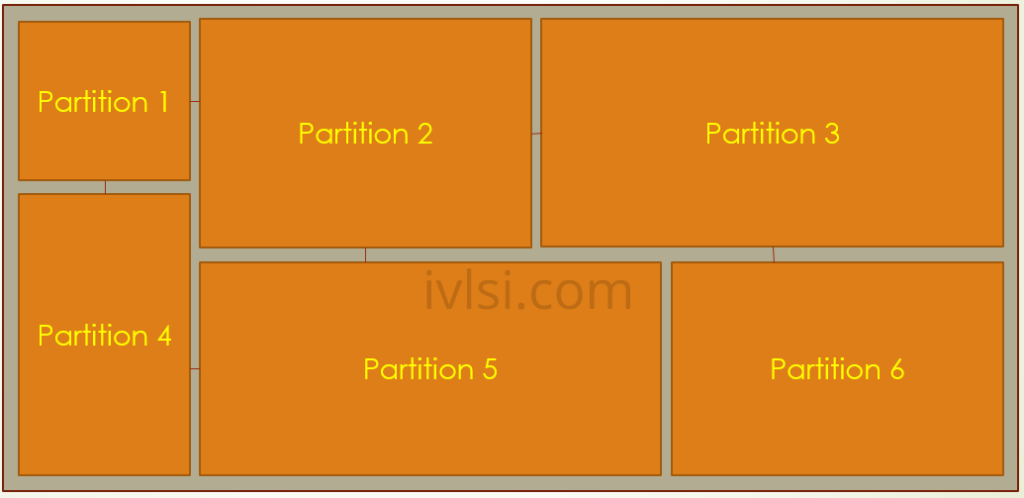

Before going into all the physical design inputs in details, I want to make you understand the block level design and Full Chip Level design (FC). Mostly, partition owners are assigned with the block-level design to work on one partition and then those partitions are being integrated by the FC owner, who assembles all the blocks to create entire Full chip-level design.

Below are the images which explain the difference between block-level and FC level design.

Full Chip Level Design