Decap Cells

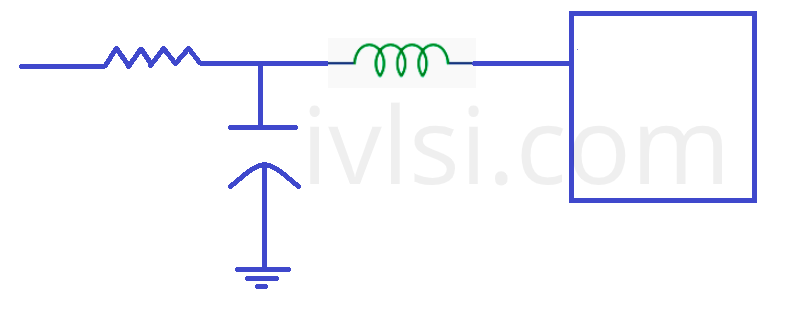

Decap cell is basically a capacitor cell which is used temporarily in the design between power and ground rails to counter the functional failure. We cant have functional failure in our design. So to avoid any kind of functional failure due to Dynamic IR, we use Decap cells in our design.

Current (I) Increases near inductor, so L d(I)/d(t) increases, due to which Voltage drop across Inductor increases, hence less voltage at the partition or logic group or registers is seen in the design. In order to avoid this condition, we put De-Cap cells which supply local current.

The functional failure occurs in the design at the active edge of clock where flop switches end up loosing data which was about to be captured. In the design all flops don’t get placed near the power source due to which the flops go into Metastable state, which means circuit is unable to get settled into state ‘0’ or ‘1’ logic level within the required time. To avoid this metastable state, we use decap cell which helps in boosting power and reducing IR drop when required.

De-cap cells are poly gate transistor where source and drain are connected to the ground rail and gate is connected to the power rail.

De-Cap cells are leakier so more number de-cap cells in the design leads to more leakage power.