What is Synthesis?

Synthesis comes between the RTL Design & Verification and Physical design steps in VLSI. The meaning of synthesis is the transformation of a level of idea into another. To give an overview, let me clarify few points w.r.t flows before digging into Synthesis. RTL Design is the step where front-end engineers write the code in various languages such as Verilog, system Verilog, VHDL etc., and verify these codes (verification stage). Once the RTL code gets verified, then we take this RTL to next stage of VLSI Design known as Synthesis. At this stage, we convert logic codes into the circuit.

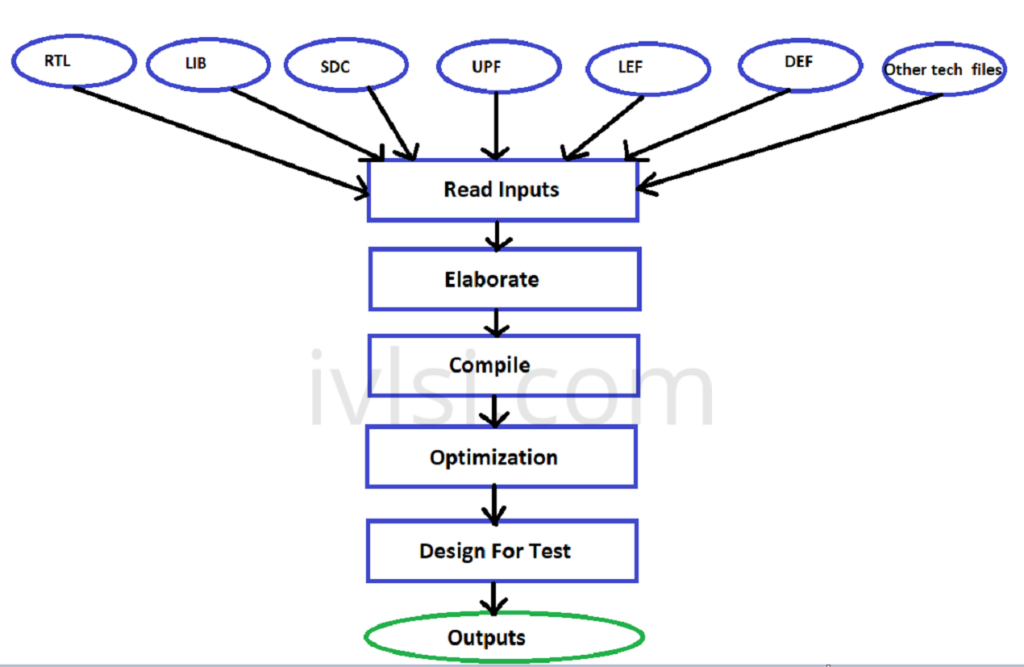

Synthesis Flow

Synthesis Inputs

1. Register Transfer Level (RTL)

2. Timing Library (LIB)

3. Standard/Synopsys Design Constraint (SDC)

4. Unified Power Format (UPF)

5. Physical Library (LEF)

6. Design Exchanged Format (DEF)

7. Other Tech files

1. Register Transfer Level (RTL)

Since this is a very huge topic, I will provide the basic details which should be enough for the synthesis or physical design candidate. RTL can be written in many languages like Verilog, VHDL, System Verilog etc. All these languages are quite similar. Let’s investigate Verilog language.

Let’s understand this with few codes.

Adder Circuit

module full_adder ( input [3:0] a,

input [3:0] b,

input c_in,

output c_out,

output [3:0] sum) ;

assign {c_out, sum} = a + b + c_in;

endmodule

D Flip-Flop

module d_ff ( input d, input rst, input clk, output reg q); always @(posedge clk or negedge rst) if (!rst) q <= 0; else q <= d; endmodule

The above codes have been written logically which has no circuit information. We need to synthesize this code to a circuit level.

2. Timing Library (LIB)

I have already explained about timing library in physical design inputs section. We use same library for synthesis as well. Here is the link:

3. Standard/Synopsys Design Constraint (SDC)

Below is the link explaining about the SDC:

4. Unified Power Format (UPF)

Below link explains about the UPF very well:

5. Physical Library (LEF)

Below link explains about the LEF very well:

6. Design Exchanged Format (DEF)

For physical synthesis DEF is a must input. This DEF contains the floorplan information of the design and it doesn’t contain the information about the objects which we have at physical design steps. Below is the link explaining about the DEF very well: